LVDS

LVDS - Low Voltage Differential Signal

// Ыхыхыхыхых писька ыхыхыхыхыых

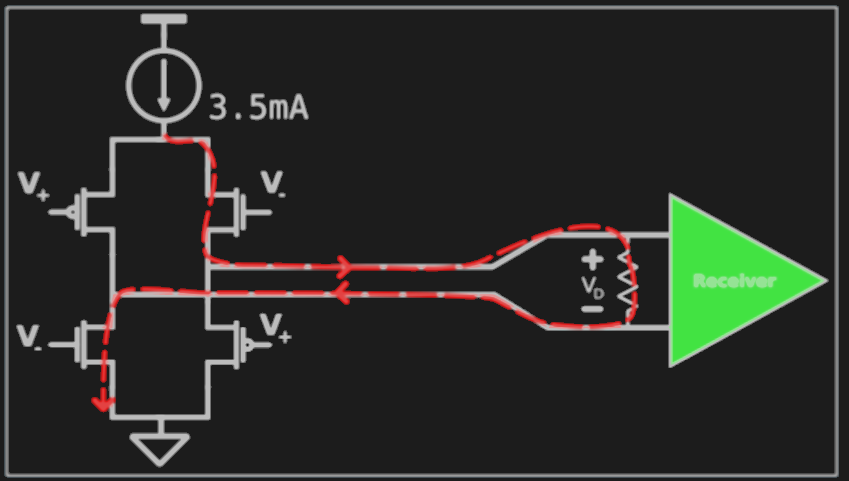

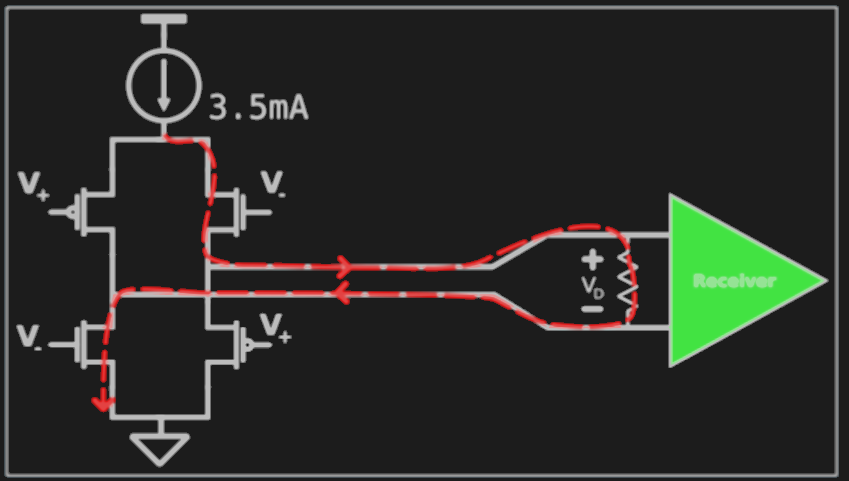

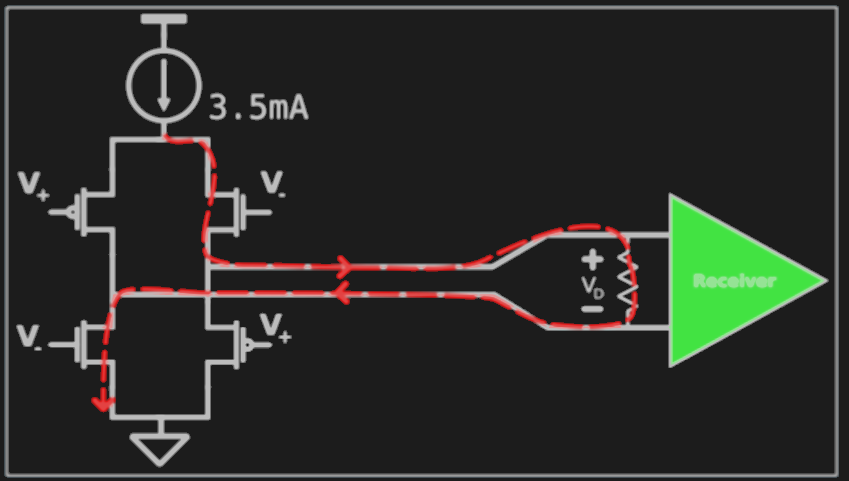

Передающая сторона (Driver)

- Источник постоянного тока -> к двум выходым линиям черещ

MOSFET-транзисторы

- Сигнал - разность напряжений между линиями

- Логический 1 - +350 мВ на линии А, -350 мВ на линии В

- Логический 0 - -350 мВ на линии А, +350 мВ на линии В

Принимающая сторона (Receiver)

- Диф. усилитель сравнивает напряжения на линиях TX+ & TX-

- Нагрузочный рещистор (100 Ом) между линиями завершает диф. пару

Ключевые параметры

- Размах каждого сигнала +-350 мВ

- Скорость передачи - до 3.125 Гбит/с на одну пару

Преимущества диф. передачи

- Низкое энергопотребление - ток через нагрузку всего 3.5 мА ->

Мощность около 11.5 мВт

- Высокая скорость - малая амплитуда сигнала позволяет быстрее

перключать состояния

- Снижение EMI (электромагнитных помех) - противоположные токи в диф.

линиях компенсируют магнитные поля

Примеры применения LVDS:

- PCIe (до 5 поколения)

- Линии - 1-16 пар в зависимости от версии

- Скорость

- Gen 4 - 16 ГТ/с на линию (ГТ - Гига Трансферы, полезные переносы

информации)

- Gen 5 - 32 ГТ/с на линию

- Gen 7 - 128 ГТ/с на линию (но там уже не LVDS лол)

- SATA (Serial ATA)

- 2 пары линий (приём-передача)

- Скорость - SATA III - 6Гбит/с

- HDMI

- Линии - 3 пары видео, 1 пара тактирования

- Скорость - HDMI 2.1 - до 48 Гбит/с (с использованием LVDS-like

технологии TMDS)

- Мобильные дисплеи (eDP)

- 1-4 пар линий

- Скорость до 8.1 Гбит/с на пару

Сравнение LVDS с другими стандартами диф.

передачи

| Параметр |

LVDS |

RS-422 |

CML |

| Напряжение питания |

3.3 В |

5 В |

2.5-3.3 В |

| Скорость |

до 3.125 Гбит/с |

До 10 Мбит/с |

До 10 Гбит/с |

| Потребление |

Низкое |

Среднее |

Высокое |

| Применение |

Дисплеи, PCIE |

Промышленность |

Сети, SerDes |

Согласование уровней

TTL, CMOS,

LVCMOS, LVDS - как их связать то блять?

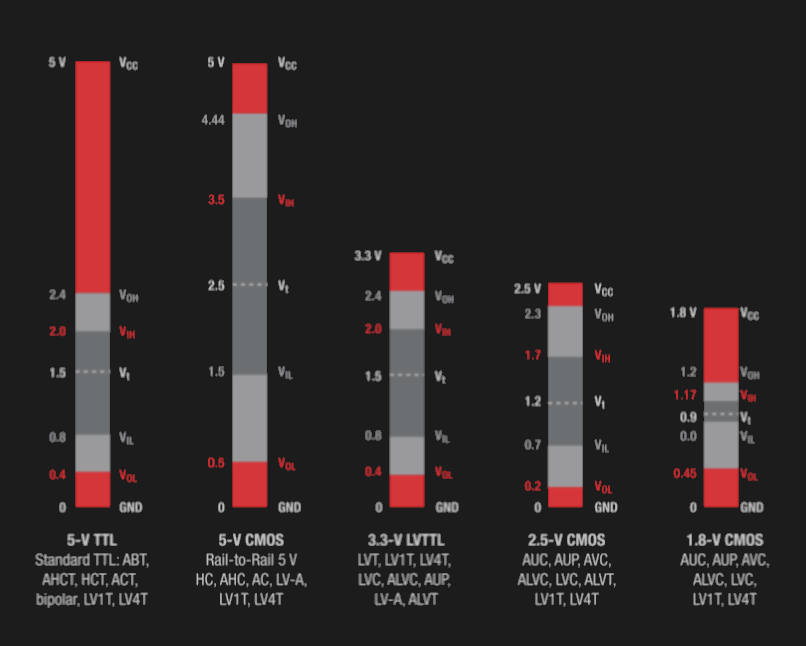

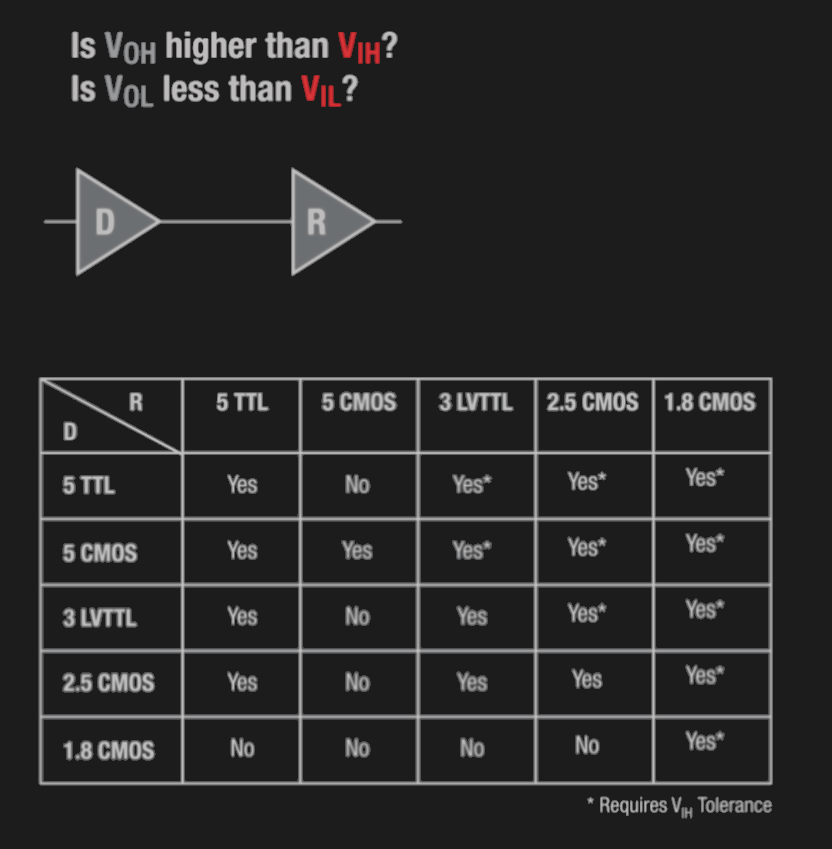

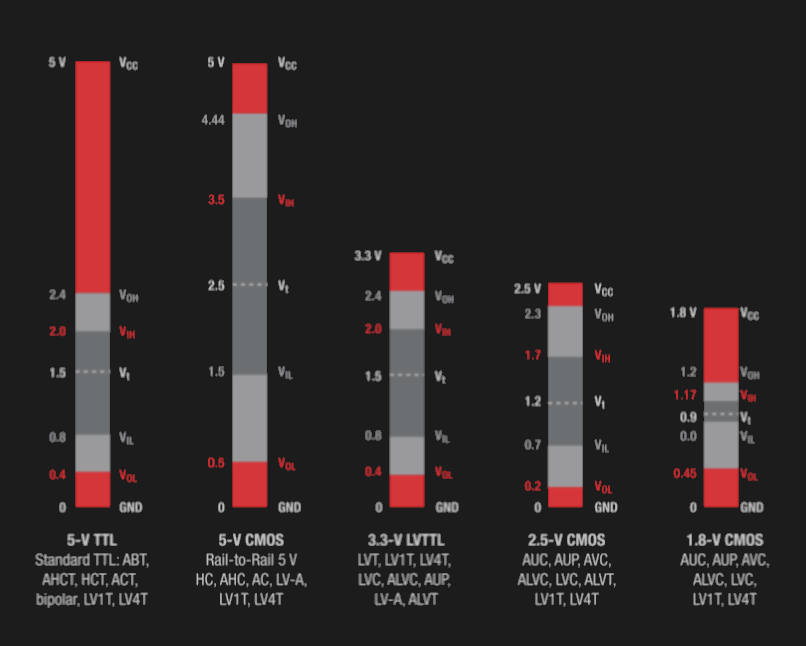

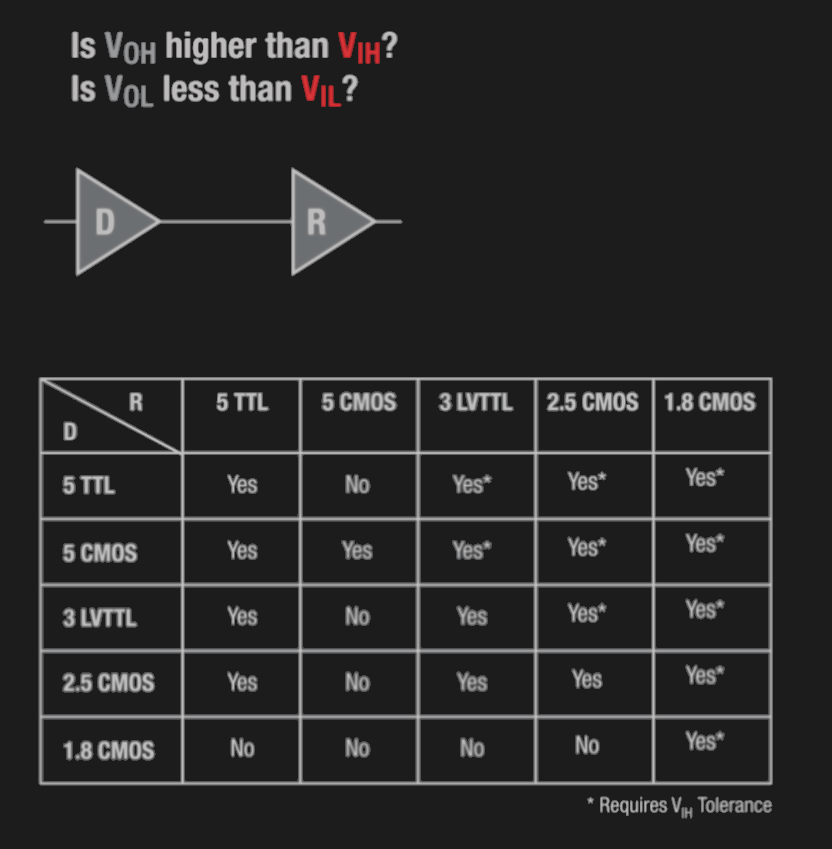

Согласование логических стандартов - важная задача при проектировании

систем, где используются компоненты с разными уровнями напряжения и

требованиями к сигналам

^ диаграмма, кто какие напряжения принимает за нули-единицы

^ Таблица совместимостей сигналов

Универсальные методы

согласования уровней

Согласование CMOS/LVCMOS и

LVDS

Проблемы:

- CMOS - односторонний сигнал (однофзный, несимметричный, с общей

землёй, single-ended) - 0-5 В

- LVCMOS - односторонний сигнал (0-1.8 В)

- LVDS - дифференциальный сигнал (+-350 мВ)

Методы согласования:

- Преобразователь CMOS/LVCMOS -> LVDS - микросхемы по типу

DS90LV011A

- Преобразователь LVDS -> CMOS/LVCMOS - микросхемы по типу

DS90LV012A

Согласование TTL и LVDS

Проблемы:

- TTL - односторонний сигнал (0-5 В)

- LVDS - диф. сигнал (+-350 мВ)

Методы согласования:

- Преобразователь TTL -> LVDS //революционно

Используются микросхемы по типу SN65LVDS1

- Преобразователь LVDS -> TTL - микросхемы по типу SN65LVDS2

Практические вопросы

Проблема

объединения выходов логических схем на шину

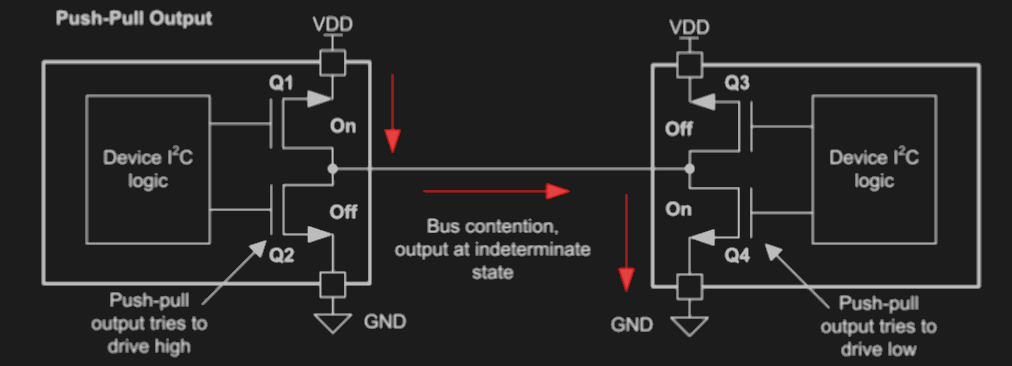

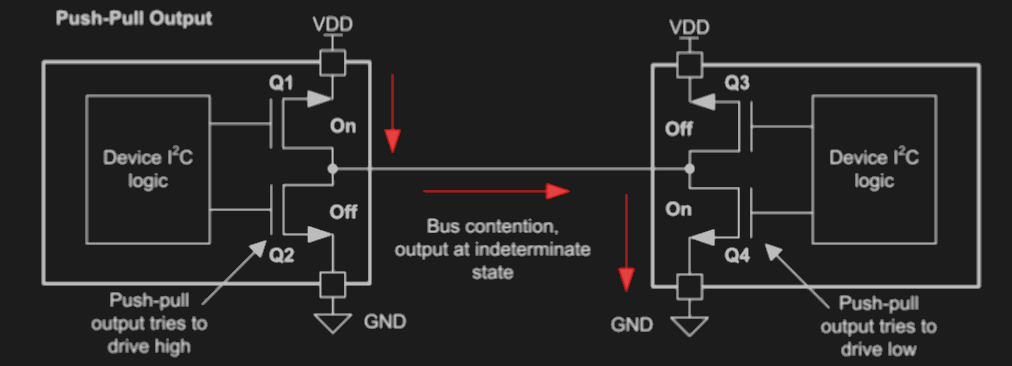

- При объединении выходов push-pull нескольких логических элементов

все формируют активный уровень

- Никто не может "освободить" шину

- При формировании разных лог. уровней двумя элементами в один момент

времени - КЗ пизда туши свет и пожар в квартире

"Выход с тремя состяниями"

- Логическая 1

- Логический 0

- Третье состояние (оно же tri-state, z-состояние, высокоимпедансное

состояние)

Третье состяние - состояние, когда схема электрически отключена от шины

(высокий импеданс)

Особенности третьего состояния выхода:

- Не формирует ни 0 ни 1

- Позволяет нескольким устройствам работать на одной шине не

конфликтуя

- Активируется сигналом Output Enable (OE)

- Пример - шина данных в МПС

Выходы GPIO МК

TTL

- С общим коллектором (open collector)

- totem-pole

CMOS

- С общим стоком (open drain)

- push-pull

Открытый коллектор / Открытый

сток

Физическая реализация выхода, а не отдельное состояние

Принцип работы:

- Выход может только притягивать линию к земле (лог. 0) или переходить

в Z-состояние

- Высокий уровент (лог. 1) формируется внешним подтягивающим

резистором

Ключевая особенность - всегда два состояния - 0 и Z

Примеры - шины

,

1-Wire